12G-SDI物理层分析之-抖动

2020年09月17日

抖动,作为12G-SDI的重要指标之一,与上升/下降时间和幅度并列为SDI三大重要指标,同时也是所有高速信号的重要指标,以用来衡量高速信号的稳定性和可靠性。对于抖动的分析,很难有特定的分析理论支持,因为抖动的生成有非常多的因素,我们首先以板级参数来分析抖动的形成。

12G-SDI(或所有高速信号)的寄生参数,一直以来都是硬件工程师最为头疼的事情,寄生电阻、寄生电感和寄生电容的存在无时无刻将高速信号拉入深渊,导致SDI的上升时间增加,边沿变缓,幅度降低和大量的抖动的生成,从而造成误码。

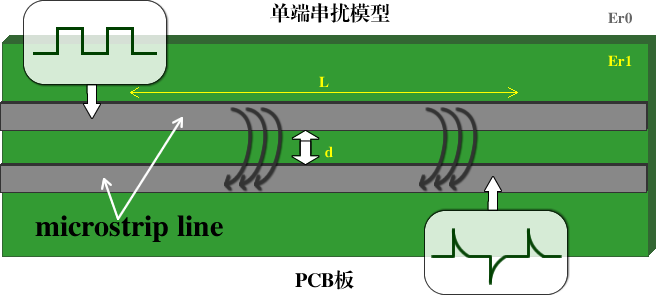

在标准大气压力和温度下,寄生参数无法去除,对于超导环境下的金属及纤维的本质变化,我们暂不考虑分析。我们可以通过一个简单的公式展开理解,以板级寄生电容公式为例:”C(pF)=W*L*Er0*Er1/d”,其中W=布线宽度,L=线长,Er0=空气介电常数,Er1=电路板的介电常数d=布线间距。可以看到,诸多参数的相互影响,构成寄生电容参数。当信号高速变化时,就会串扰至相邻走线中产生耦合电流:“I(A)=C(dV/dt)”,如果我们分析来抑制这个瞬间电流,又会出现其他问题:无论如何改变源端内阻,都会改变传输线的阻抗,形成反射导致抖动的生成;如果增加电感值,虽会抑制瞬间电流的形成,但会形成阻尼震荡磁场,对于高速信号来讲,又是致命的参数。在加上寄生电阻和寄生电感的等效阻抗的影响,12G-SDI的板级反射点非常多,从而导致大量的信源抖动的生成,并沿传输路径向后级叠加传播。

但是,信源抖动并不是12G-SDI的唯一抖动源,SDI的最大抖动源,仍然来自理想占空比周期信号的时间偏差,称为TIE(时间间隔错误)。

不同于3G/HD/SD-SDI等低速信号,12G-SDI的工作时钟频率非常高,而传输介质的影响更为严重,板级寄生参数、串扰、不匹配的阻抗以及不标准的连接器及端点焊接方式等等,都会造成12G-SDI大量的抖动生成,TIE的频域覆盖广泛,无法有效的测量和控制抖动范围,因此SMPTE 2082-1:2015 中规定了从10Hz(定时抖动下频带边缘)到1.2GHz(上频带边缘)之间的抖动定义为定时抖动(Timing Jitter),而100KHz(对齐抖动下频带边缘)到1.2GHz(上频带边缘)之间的抖动定义为对齐抖动(Alignment Jitter)。测量由TIE引起的抖动,是目前测试12G-SDI最有效的方法,同时也适用于6G/3G/HD/SD-SDI和符合地面数字广播DVB-ASI(MPEG2及H.264、AVS/+等)编码的TS流的测试。

可以看出,定时抖动(Timing Jitter)因其覆盖更广泛的频域,所以抖动数值要大于对齐抖动(Alignment Jitter)。按照ST2082-1:2015的执行标准,12G-SDI的定时抖动值应小于2UI(168ps),而对齐抖动值应小于0.3UI(28ps)。

在这里,我们引入另外两个名称:确定性抖动和随机抖动。

由于生成抖动的因素非常之多,为了方便抖动的归类,我们把具有可重复性周期及可预测性的抖动,称为确定性抖动;把随时间的变化而变化的具有不确定性的符合高斯分布的抖动,称之为随机抖动。而由于随机抖动无法有效的过滤和去除,在测量12G-SDI抖动时,仍会受到其影响,导致测试值波动从而超出ST标准。在此同样建议产品设计者尽可能优化板级设计,匹配阻抗特性,提高12G-SDI抖动裕度,降低输出抖动。

在所有SMPTE的SDI标准中,首次将12G-SDI的对齐抖动放宽至0.3UI,虽比3G-SDI的0.2UI的标准增加了0.1UI,但4倍于3G-SDI速度的12G-SDI,0.1UI的增加,对于抖动的余量,其作用仍然微乎其微。如何有效的降低信号抖动,仍是产品设计者最严峻的考验。

[技术文章版权所有,转载请注明出处]